intoPIX ,提供各种可能性来评估JPEG XS技术,我们的IP-cores和加速软件库。

我们的团队拥有丰富的经验,可以支持客户加速整合成一个功能齐全的系统。

试试我们的参考软件和SDKs

试试我们的参考软件和SDKs

获取TicoXS参考软件的可执行文件,包括所有JPEG XS配置文件和intoPIX 高质量编码。这个参考软件超过了基线JPEG XS参考软件的质量,使你能够评估压缩效率。

直接进入intoPIX FastTicoXSSDKs 的试用版,用于CPU 或GPU 。

这种商业 库 在速度上进行了高度优化,既能满足高像素率的最高要求,又能满足极低的延时。 此外,SDKs 已经与第三方库集成,如Nvidia RivermaxSDK forSMPTE 2110, FFmpeg等。

试试我们的FPGA 开发套件

试试我们的FPGA 开发套件

intoPIX ,通过视频应用参考设计/概念验证加速客户的产品开发。这些参考设计旨在利用intoPIX的高性能TicoXS IP-cores提供一个强大的概念证明。

我们为Intel & AMD-Xilinx FPGA提供参考设计。

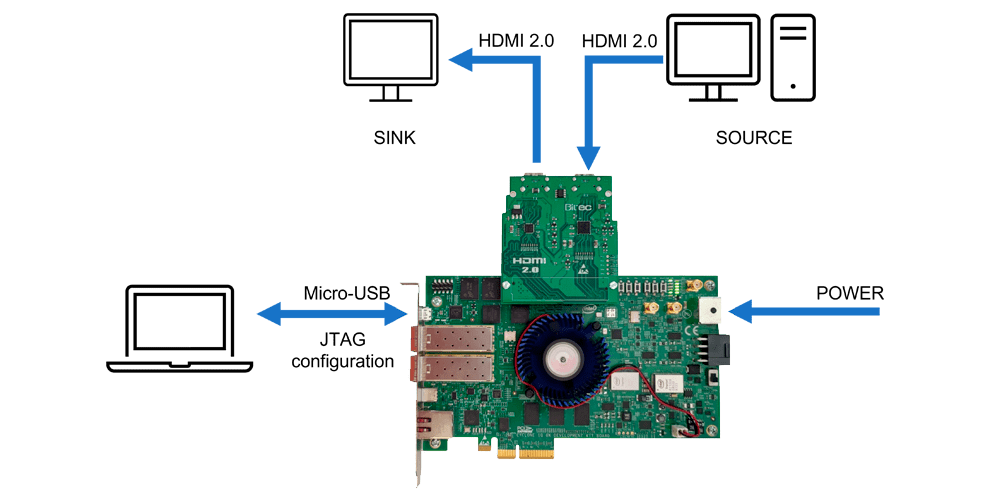

基于Altera Cyclone 10或Arria 10FPGA的紧凑型HDMI 2.0 4K参考设计

intoPIX 与 Altera 合作intoPIX Altera® Cyclone® 10 GX 或 Arria® 10 SoC 开发套件上提供基于该标准的评估设计:这为您的嵌入式视频和图像处理应用测试及实现JPEG 配置文件或intoPIX Flawless Imaging 配置文件,为您的嵌入式视频和图像处理应用提供便捷的测试与实现方案。

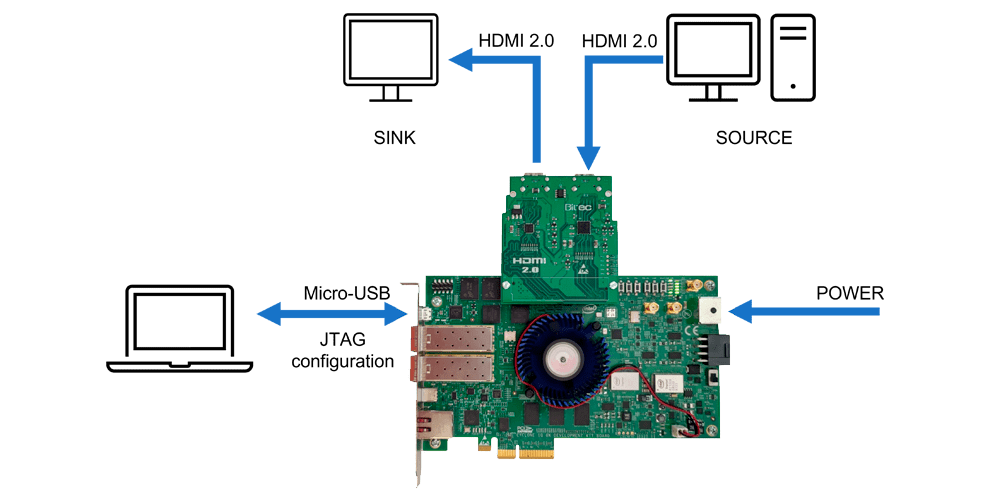

该示例设计面向 Altera® Cyclone® 10 GX 或Arria® 10 SoCFPGA 套件。该设计基于 Altera HDMI 环回示例设计,通过连接至开发套件的 FMC 连接器上的 HDMI 中间层子卡,提供 HDMI 2.0 视频输入/输出接口。 在 Altera HDMI 2.0IP之间引入了基于 TicoXSIP JPEG 4K 60fps 编解码器链,并通过 JTAG 连接允许用户调整intoPIX 压缩比。Arria 10 SoC 设计还在JPEG High 配置文件的基础上,额外支持Flawless Imaging 。

特征

- 易于评估intoPIX 编解码器 的质量、延迟,在各种压缩率下使用实时编码-解码回环。

- 在Cyclone 10开发套件上,TicoXS编码器/解码器(JPEG XS High profile)可达到UHD4K每秒60帧(fps)444/422

- 在Arria 10开发套件上,TicoXS FIP编码器/解码器 (JPEG XS High profile与Flawless Imaging profile)和高达UHD4K 60帧/秒(fps)444/422。

- 适用于以边缘为中心的FPGA的紧凑实现 .

- 可配置的编解码器设置使你能够评估不同的带宽和压缩率。

好处

- FPGA评估intoPIX 简便方法,仅需一个 Altera Cyclone® 10 GX 或Arria® 10 SoC开发套件,以及一块 HDMI 2.0 FMC 子卡。

- 完整的 Altera /Intel 解决方案:在您的嵌入式FPGA 使用与 intoPIX IP ,并在您的CPU 中使用 intoPIX 开发工具包 (SDK) 实现。

Intel Cyclone 10、Arria 10 或 Agilex 7 FPGA 上的紧凑型 HDMI 2.0 4K 和 HDMI 2.1 8K 示例设计

与Intel 合作,intoPIX 在英特尔® Cyclone® 10 GX、Arria®10 或 Agilex® 7FPGA SoC 开发套件:为您的嵌入式视频和图像处理应用测试和实施JPEG XS 配置文件或intoPIX Flawless Imaging pXS 配置文件或 p97 配置文件。

该示例设计针对英特尔® Cyclone® 10 GX或Arria® 10 SoC FPGA 开发套件。基于Intel HDMI环回实例设计,它使用HDMI 2.0视频输入/输出,通过一个FMC连接器连接到开发套件的夹层HDMI子卡。JPEG XS 4K 60fps编码器-解码器链被引入Intel HDMI 2.0IP-核之间,使用TicoXS IP-核,通过JTAG连接允许用户调整intoPIX 编解码器的压缩率。Arria 10 Soc设计的特点是在JPEG XS高配置的基础上增加了Flawless Imaging 配置。

该示例设计针对 Intel® Agilex® 7SoC FPGA 开发套件。它基于Intel HDMI 回环示例设计,使用通过 FMC 连接器连接到开发套件的夹层 HDMI 子卡访问 HDMI 2.1 视频输入/输出。Intel HDMI 2.1IP 内核与 TicoXSIP 内核之间引入了JPEG XS 8K 60fps 编码器-解码器链,通过 JTAG 连接,用户可以调整intoPIX 编解码器的压缩率。在 JPEG XS HIGH 配置文件和JPEG XS TDC 配置文件的基础上,Agilex Soc 设计 还采用了Flawless Imaging 配置文件。

特征

- 易于评估intoPIX 编解码器 的质量、延迟,在各种压缩率下使用实时编码-解码回环。

- 在 Cyclone 10FPGA Dev Kit 上,TicoXS 编码器/解码器(JPEG XS High profile)最高可达 UHD4K 60 帧/秒 (fps) 444/422

- 在 Arria 10 FPGA开发套件,TicoXS FIP 编码器/解码器 (JPEG XS 高配置文件与Flawless Imaging 配置文件),高达 UHD4K 60 帧/秒 (fps) 444/422

- 在 Agilex 7 FPGA开发套件上,TicoXS 编码器/解码器(JPEG XS 高和 TDC 配置文件最高可达 UHD8K 每秒 60 帧 (fps) 444/422/420

- 适用于以边缘为中心的FPGA的紧凑实现 .

- 可配置的编解码器设置使你能够评估不同的带宽和压缩率。

好处

- 在FPGA 中评估intoPIX IP 的简便方法,只需要一个Intel Cyclone® 10 GX 或 Arria® 10SoC 开发套件 + 一个 HDMI 2.0 FMC 子卡。

- 仅需要Intel Agilex 7FPGA I 系列收发器-SoC 开发套件(4x F-Tile)和 HDMI 2.1 FMC 子卡:一块电路板实现了编码-解码环回。

- 完整的Intel 端到端解决方案:在您的嵌入式FPGA 设计中使用相同的视频编解码器,并使用 intoPIX 硬件IP和在你的CPU 设计中使用相同的视频编解码器,并使用 intoPIX 软件开发工具包(SDK)。

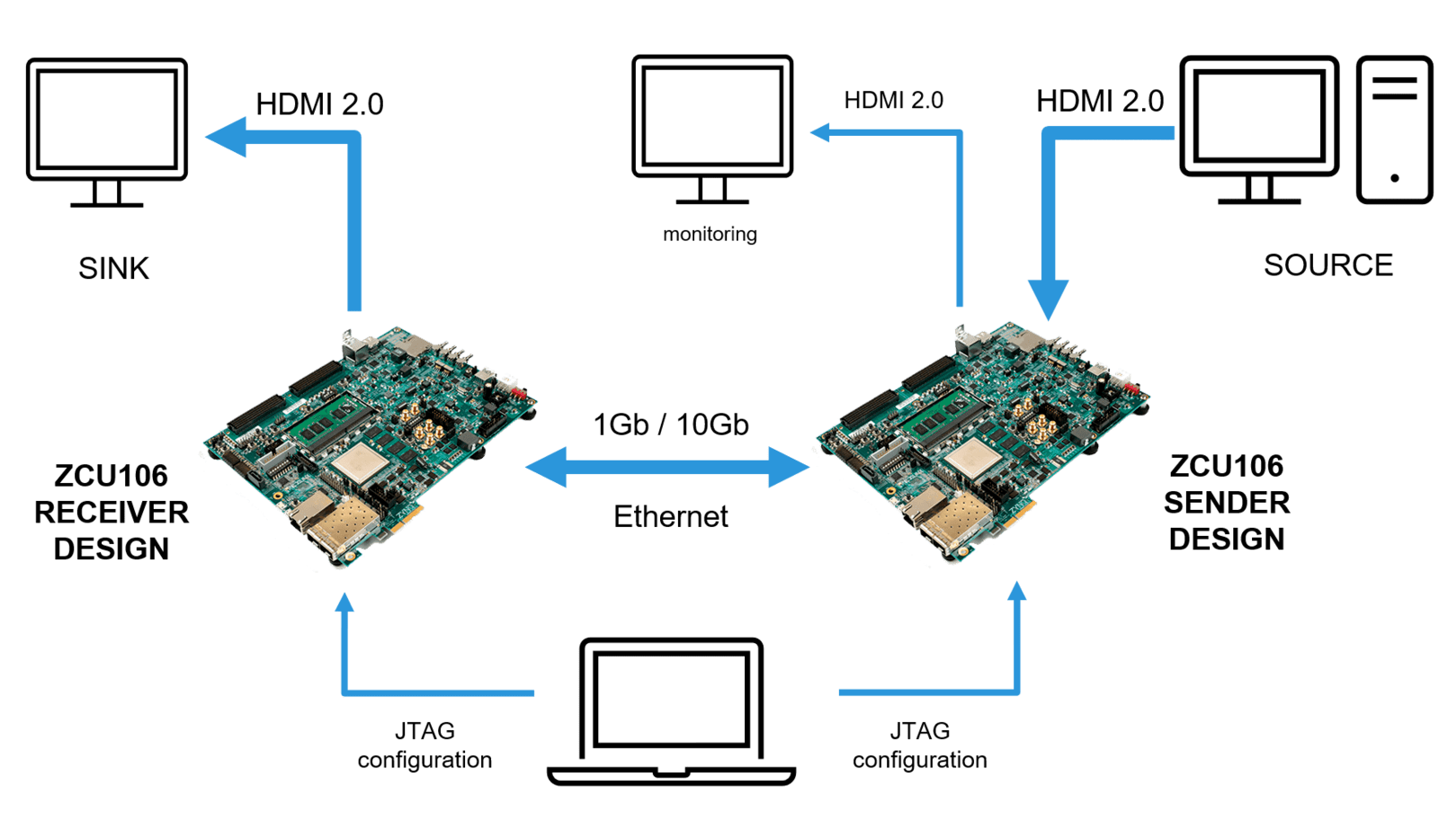

IP 4KSMPTE 2110-22 在AMD-Xilinx ZCU106FPGA 上的低延迟,带有TicoXS或TicoXS FIP编码器/解码器内核的例子设计。

IP 4KSMPTE 2110-22 在AMD-Xilinx ZCU106FPGA 上的低延迟,带有TicoXS或TicoXS FIP编码器/解码器内核的例子设计。

特征

特征

- 在不同的压缩率下,使用独立的发送器和接收器设计,对完整的压缩视频传输流进行评估。

- 适用于以边缘为中心的FPGA的紧凑实现,不需要为压缩方案提供外部DDR存储器。

- Xilinx (AMD) HDMI 2.0 TX和RX子系统。

- IntoPIX TicoXS IP-coresup to UHD4K 60 frames per second (fps) 444/422 encoder and decoder IP-cores for JPEG XS High profile.

- IntoPIX TicoXS FIPIP-coresup to UHD4K 60 frames per second (fps) 444/422 encoder and decoderIP-cores forJPEG XS High profile withFlawless Imaging profile.

- intoPIX TicoXS RTP有效载荷IP-cores 在SMPTE ST2110-22中定义,用于VSF TR08建议的独立RTP精华传输。

- Xilinx (AMD)以太网与10GBE或1GBE RX & TX子系统。

- 可配置的编解码器设置使你能够评估不同的带宽和压缩率。

好处

- 这是一个起点,用于评估在兼容的SMPTE 2110-22IP 网络上的实际低延迟压缩视频传输,只需要两个Xilinx (AMD) ZCU106开发套件和适当的SFP。

- 编码器/解码器和RTPIP-cores由intoPIX 完全集成到Xilinx (AMD)框架中。

支持和定制服务

支持和定制服务

凭借反应能力、预见性和可用性,intoPIX ,围绕其IP-cores和SDKs 的整合提供支持服务。这些服务非常适用于任何类型的视听系统的生命周期。intoPIX ,帮助您加快进入市场的时间,并为您的应用确定最合适的解决方案。

intoPIX 发展支持保证:

- 确保与 intoPIX

- 具体了解您的环境、设备细节和技术案例历史记录

- 接触我们的技术专家。这样,您可以快速获得任何技术问题的解答

- 更新和升级通知和支持

- 互 操作 性。 intoPIX 将确保您的系统符合当前标准

除了我们的IP 内核和SDKs 的固有灵活性外,我们知道一些应用可能包括标准集成支持范围之外的特殊要求。intoPIX 可以帮助定制标准的IP 块和软件,以满足所需的特殊需求。关于我们的定制服务的更多信息,请联系我们。